# Western Digital®

## RISC-V SweRV™ EH1 Programmer's Reference Manual

Revision 1.6

May 15, 2020

SPDX-License-Identifier: Apache-2.0

Copyright © 2020 Western Digital Corporation or its affiliates.

Licensed under the Apache License, Version 2.0 (the "License"); you may not use this file except in compliance with the License. You may obtain a copy of the License at

#### http://www.apache.org/licenses/LICENSE-2.0

Unless required by applicable law or agreed to in writing, software distributed under the License is distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License for the specific language governing permissions and limitations under the License.

## **Document Revision History**

| Revision | Date         | Contents                                                                                                                                                 |

|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | Jan 24, 2019 | Initial revision                                                                                                                                         |

| 1.1      | May 31, 2019 | Updated 'Reference Documents' table:                                                                                                                     |

|          |              | Updated link and version number of RISC-V ISA spec                                                                                                       |

|          |              | <ul> <li>Updated link and version number of RISC-V Privileged spec, updated section<br/>references throughout text</li> </ul>                            |

|          |              | Added link and version number of last RISC-V Privileged spec with PLIC chapter                                                                           |

|          |              | Fixed URL and updated version number of RISC-V Debug spec                                                                                                |

|          |              | Added core pipeline summary (Section 1.3.1)                                                                                                              |

|          |              | Corrected load-to-load ordering description (Section 2.5.1)                                                                                              |

|          |              | Added section on 'Bus Barrier' mechanism (Section 2.5.3.3) and updated instructions and data fencing sections accordingly (Sections 2.5.3.1 and 2.5.3.2) |

|          |              | Added section on 'Memory Protection' mechanism (Section 2.6)                                                                                             |

|          |              | Updated note when mrac access control bits are ignored (Section 2.8.1)                                                                                   |

|          |              | Clarified note how writing illegal value to mrac register is handled by hardware (Section 2.8.1)                                                         |

|          |              | Added region number to field names of mrac register to make them unique (Table 2-6)                                                                      |

|          |              | <ul> <li>Changed field name fence.i in dmst register to fence_i to avoid potential<br/>compatibility issues with tools (Table 2-7)</li> </ul>            |

|          |              | Added section on 'Speculative Bus Accesses' (Section 2.11)                                                                                               |

|          |              | Updated DMA QoS description (Section 2.12.3)                                                                                                             |

|          |              | <ul> <li>Added note that applied reset vector must be to valid and enabled memory address<br/>(Section 2.13)</li> </ul>                                  |

|          |              | Updated NMI description and added table of mcause values (Section 2.14)                                                                                  |

|          |              | Clarified comment about stuck-at bits (Section 3.4)                                                                                                      |

|          |              | Corrected note regarding correctable error local interrupt not being latched (Sections 3.5.1, 3.5.2, and 3.5.3)                                          |

|          |              | Updated Power Management chapter (Chapter 5):                                                                                                            |

|          |              | Changed title to 'Power Management and Multi-Core Debug Control'                                                                                         |

|          |              | <ul> <li>Added brief descriptions of power management unit (PMU) and multi-processor<br/>debug control (MPC) interfaces (Section 5.2)</li> </ul>         |

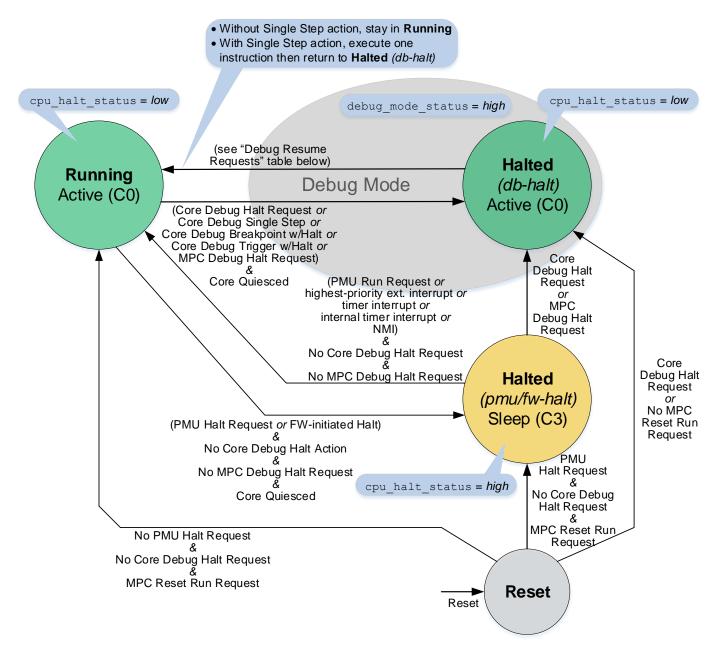

|          |              | Clarified that only highest-priority external interrupt wakes up core (Figure 5-1)                                                                       |

|          |              | Updated note describing 'Core Quiesced' (Section 5.3)                                                                                                    |

|          |              | Added notes how to tie off input signals if PMU interface not used (Table 5-3)                                                                           |

|          |              | Added notes how to tie off input signals if MPC interface not used (Table 5-4)                                                                           |

|          |              | Updated cross-reference to mhwakeup signal description to be more precise     (Section 5.4.7)                                                            |

|          |              | Clarified vectored external interrupt handler selection steps (Section 6.6)                                                                              |

|          |              | Added source ID to field names of meipX register to make them unique (Table 6-3)                                                                         |

|          |              | Clarified that event counting of division instructions includes remainder instructions (Table 7-2)                                                       |

|          |              | Fixed note on tag alignment (Table 8-2)                                                                                                                  |

|          |              | Updated mfdc register definition (Table 10-1):                                                                                                           |

|          |              | Updated field descriptions                                                                                                                               |

| Revision | Date         | Contents                                                                                                                                   |

|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|          |              | Assigned names to fields                                                                                                                   |

|          |              | Added 'DMA QoS control' field                                                                                                              |

|          |              | Added 'side effect posted disable' bit                                                                                                     |

|          |              | Removed 'PIC multiple interrupts disable' bit (was bit 9)                                                                                  |

|          |              | Removed 'Load miss bypass Write Buffer (WB) disable' bit (was bit 1)                                                                       |

|          |              | Updated mcgc register definition (Table 10-2):                                                                                             |

|          |              | Updated field descriptions                                                                                                                 |

|          |              | Assigned names to fields                                                                                                                   |

|          |              | Improved clarity of mcause value table (Table 11-3)                                                                                        |

|          |              | Updated asynchronous signals (Table 14-1):                                                                                                 |

|          |              | Removed core output signals                                                                                                                |

|          |              | Added that JTAG signals are synchronous to TCK                                                                                             |

|          |              | Added asynchronous MPC interface signals                                                                                                   |

|          |              | Updated port list (Table 15-1):                                                                                                            |

|          |              | Removed '(async)' label from core output signals                                                                                           |

|          |              | Added missing DMA Slave AHB-Lite bus signals                                                                                               |

|          |              | Added MPC interface signals                                                                                                                |

|          |              | Updated performance counter activity signals                                                                                               |

|          |              | Added that JTAG signals are synchronous to TCK                                                                                             |

|          |              | • Added jtag_id port                                                                                                                       |

|          |              | Added 'Memory Protection Build Arguments' (Section 16.1)                                                                                   |

|          |              | Updated 'Errata' chapter (Chapter 18):                                                                                                     |

|          |              | Added 'Back-to-back Write Transactions Not Supported on AHB-Lite Bus' section                                                              |

|          |              | Removed 'Core May Handle Write Transactions with Different Transaction IDs<br>Incorrectly on AXI System Bus' section, issue has been fixed |

| 1.2      | Aug 13, 2019 | Updated bus barrier description (Section 2.5.3.3)                                                                                          |

|          |              | Updated ICCM/DCCM error detection and handling details (Table 2-4 and Table 2-5)                                                           |

|          |              | Added clarification that ordering between core and DMA accesses is not guaranteed (Section 2.12.4)                                         |

|          |              | Updated ICCM/DCCM recovery/logging details (Table 3-2)                                                                                     |

|          |              | Clarified that correctable errors on DMA reads to ICCM/DCCM are counted (Sections 3.5.2 and 3.5.3)                                         |

|          |              | Clarified that correctable DCCM errors counted only for retired load/store instructions (Section 3.5.3)                                    |

|          |              | Changed 'RV_' prefix to '`RV_' (Table 14-1)                                                                                                |

|          |              | Updated port list (Table 15-1):                                                                                                            |

|          |              | Changed 'RV_' prefix to '`RV_'                                                                                                             |

|          |              | Added 'core_rst_l' signal                                                                                                                  |

|          |              | Removed 'mbist_mode' signal                                                                                                                |

| Revision                             | Date         | Contents                                                                                                                  |

|--------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------|

| 1.5                                  | Feb 14, 2020 | Added footnote that PIC access errors also included (Table 2-2)                                                           |

|                                      |              | • Clarified that correctable error local interrupt is level signaled (Sections 3.5.1, 3.5.2, and 3.5.3)                   |

|                                      |              | Fixed scope of Debug Mode in Core Activity States diagram (Figure 5-1)                                                    |

|                                      |              | Added several clarifications on MPC interface restrictions:                                                               |

|                                      |              | <ul> <li>Halt/run request typically allowed only when not in requested state already<br/>(Section 5.3)</li> </ul>         |

|                                      |              | Signaling same request multiple times not allowed (Table 5-4)                                                             |

|                                      |              | Conditions when requests are acknowledged (Section 5.4.2.2)                                                               |

|                                      |              | <ul> <li>After reset to Debug Mode, run request only allowed after core is in Debug Mode<br/>(Section 5.4.2.2)</li> </ul> |

|                                      |              | Added Single Stepping section (Section 5.4.1.1)                                                                           |

|                                      |              | Amended note regarding signaling PMU halt/run request when already in that state (Section 5.4.2.1)                        |

|                                      |              | Added note that interrupts must be disabled while changing some interrupt registers (Section 6.5)                         |

|                                      |              | Updated mimpid register value to '2' (Table 12-1)                                                                         |

|                                      |              | Added standard CSR address map (Table 12-2)                                                                               |

|                                      |              | Updated port list (Table 15-1):                                                                                           |

|                                      |              | Added dbg_rst_l signal                                                                                                    |

|                                      |              | <ul> <li>Removed core_rst_1 signal (signal on core periphery, but not core complex periphery)</li> </ul>                  |

|                                      |              | Removed sb_axi_arsize bus description comment indicating 'hardwired'                                                      |

|                                      |              | <ul> <li>Added mbist_mode signal (signal on core complex periphery, but not core periphery)</li> </ul>                    |

|                                      |              | Added 'Compliance Test Suite Failures' chapter (Chapter 17)                                                               |

|                                      |              | Added erratum for debug access register abstract command issue (Section 16.2)                                             |

| 1.5.1                                | Feb 28, 2020 | Added note that uninitialized DCCM may cause loads to get incorrect data (Section 3.4)                                    |

| Added Debug Module reset description |              | Added Debug Module reset description (Section 14.3.2)                                                                     |

|                                      |              | Added footnote clarifying trace port signals (Table 15-1)                                                                 |

|                                      |              | Added erratum for access register abstract command size check issue (Section 16.3)                                        |

| Revision | Date         | Contents                                                                                                                                                    |

|----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.6      | May 15, 2020 | Added footnote that misaligned accesses to side-effect regions trigger a misaligned exception instead of the recommended access fault exception (Table 2-3) |

|          |              | Fixed note how writing illegal value to mrac register is handled by hardware (Section 2.8.1)                                                                |

|          |              | Added Internal Timers chapter and references throughout document (Chapter 4)                                                                                |

|          |              | <ul> <li>Added cross-references to debug CSR descriptions (Table 5-2, Table 5-4, Table<br/>12-2, and Sections 7.4 and 14.3.4)</li> </ul>                    |

|          |              | Added Debug Support chapter (Chapter 9)                                                                                                                     |

|          |              | • Incremented mimpid register value from '2' to '3' (Table 12-1)                                                                                            |

|          |              | Updated 'Errata' chapter (Chapter 18):                                                                                                                      |

|          |              | <ul> <li>Removed erratum for debug access register abstract command issue (fixed) (was<br/>Section 16.2)</li> </ul>                                         |

|          |              | <ul> <li>Removed erratum for access register abstract command size check issue (fixed)<br/>(was Section 16.3)</li> </ul>                                    |

|          |              | Added erratum for debug write to minstret register issue (Section 18.2)                                                                                     |

|          |              | Added erratum for abstract command register read capability (Section 18.3)                                                                                  |

## **Table of Contents**

| 1 | Swe  | PRV EH1 Core Overview                                 | 1   |

|---|------|-------------------------------------------------------|-----|

|   | 1.1  | Features                                              | 1   |

|   | 1.2  | Core Complex                                          | 1   |

|   | 1.3  | Functional Blocks                                     | 2   |

|   | 1.3. | 1 Core                                                | 2   |

| 2 | Mer  | mory Map                                              | 3   |

|   | 2.1  | Address Regions                                       | 3   |

|   | 2.2  | Access Properties                                     | 3   |

|   | 2.3  | Memory Types                                          | 3   |

|   | 2.3. | 1 Core Local                                          | 3   |

|   | 2.3. | 2 Accessed via System Bus                             | 3   |

|   | 2.3. | 3 Mapping Restrictions                                | 4   |

|   | 2.4  | Memory Type Access Properties                         | 4   |

|   | 2.5  | Memory Access Ordering                                | 4   |

|   | 2.5. | 1 Load-to-Load and Store-to-Store Ordering            | 4   |

|   | 2.5. | 2 Load/Store Ordering                                 | 4   |

|   | 2.5. | 3 Fencing                                             | 5   |

|   | 2.5. | 4 Imprecise Data Bus Errors                           | 5   |

|   | 2.6  | Memory Protection                                     | 6   |

|   | 2.7  | Exception Handling                                    | 6   |

|   | 2.7. | 1 Imprecise Bus Error Non-Maskable Interrupt          | 6   |

|   | 2.7. | 2 Correctable Error Local Interrupt                   | 6   |

|   | 2.7. | 3 Rules for Core-Local Memory Accesses                | 7   |

|   | 2.7. | 4 Unmapped Addresses                                  | 8   |

|   | 2.7. | 5 Misaligned Accesses                                 | 9   |

|   | 2.7. | 6 Uncorrectable ECC Errors                            | .10 |

|   | 2.7. | 7 Correctable ECC/Parity Errors                       | .11 |

|   | 2.8  | Control/Status Registers                              | .12 |

|   | 2.8. | 1 Region Access Control Register (mrac)               | .12 |

|   | 2.8. | 2 Memory Synchronization Trigger Register (dmst)      | .13 |

|   | 2.8. | 3 D-Bus First Error Address Capture Register (mdseac) | .13 |

|   | 2.8. | 4 D-Bus Error Address Unlock Register (mdeau)         | .14 |

|   | 2.9  | Memory Address Map                                    | .14 |

|   | 2.10 | Partial Writes                                        | .15 |

|   | 2.11 | Speculative Bus Accesses                              | .15 |

|   | 2.11 | 1.1 Instructions                                      | .15 |

|   | 2.11 | 1.2 Data                                              | .15 |

|   | 2.12 | DMA Slave Port                                        | .15 |

|   | 2.1  | 2.1   | Access                                                       | 15 |

|---|------|-------|--------------------------------------------------------------|----|

|   | 2.1  | 2.2   | Write Alignment Rules                                        | 16 |

|   | 2.1  | 2.3   | Quality of Service                                           | 16 |

|   | 2.1  | 2.4   | Ordering of Core and DMA Accesses                            | 16 |

|   | 2.13 | R     | eset Signal and Vector                                       | 16 |

|   | 2.14 | N     | on-Maskable Interrupt (NMI) Signal and Vector                | 16 |

| 3 | Me   | mory  | Error Protection                                             | 18 |

|   | 3.1  | Ger   | neral Description                                            | 18 |

|   | 3.1  | .1    | Parity                                                       | 18 |

|   | 3.1  | .2    | Error Correcting Code (ECC)                                  | 18 |

|   | 3.2  | Sele  | ecting the Proper Error Protection Level                     | 19 |

|   | 3.3  | Mer   | mory Hierarchy                                               | 20 |

|   | 3.4  | Erro  | or Detection and Handling                                    | 20 |

|   | 3.5  | Cor   | e Error Counter/Threshold Registers                          | 22 |

|   | 3.5  | .1    | I-Cache Error Counter/Threshold Register (micect)            | 23 |

|   | 3.5  | .2    | ICCM Correctable Error Counter/Threshold Register (miccmect) | 23 |

|   | 3.5  | .3    | DCCM Correctable Error Counter/Threshold Register (mdccmect) | 24 |

| 4 | Inte | rnal  | Timers                                                       | 25 |

|   | 4.1  | Fea   | tures                                                        | 25 |

|   | 4.2  | Des   | scription                                                    | 25 |

|   | 4.3  | Inte  | rnal Timer Local Interrupts                                  | 25 |

|   | 4.4  | Cor   | ntrol/Status Registers                                       | 25 |

|   | 4.4  | .1    | Internal Timer Counter 0 / 1 Register (mitcnt0/1)            | 26 |

|   | 4.4  | .2    | Internal Timer Bound 0 / 1 Register (mitb0/1)                | 26 |

|   | 4.4  | .3    | Internal Timer Control 0 / 1 Register (mitctl0/1)            | 26 |

| 5 | Pov  | ver N | Management and Multi-Core Debug Control                      | 28 |

|   | 5.1  | Fea   | tures                                                        | 28 |

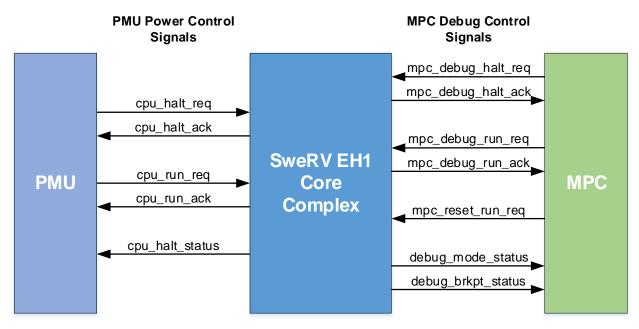

|   | 5.2  | Cor   | e Control Interfaces                                         | 28 |

|   | 5.2  | .1    | Power Management                                             | 28 |

|   | 5.2  | .2    | Multi-Core Debug Control                                     | 28 |

|   | 5.3  | Pov   | ver States                                                   | 28 |

|   | 5.4  | Pov   | ver Control                                                  | 31 |

|   | 5.4  | .1    | Debug Mode                                                   | 32 |

|   | 5.4  | .2    | Core Power and Multi-Core Debug Control and Status Signals   | 32 |

|   | 5.4  | .3    | Debug Scenarios                                              | 38 |

|   | 5.4  | .4    | Core Wake-Up Events                                          | 39 |

|   | 5.4  | .5    | Core Firmware-Initiated Halt                                 | 39 |

|   | 5.4  | .6    | DMA Operations While Halted                                  | 39 |

|   | 5.4  | .7    | External Interrupts While Halted                             | 39 |

|   | 5.5  | Cor   | ntrol/Status Registers                                       | 40 |

| 5.5  | 5.1    | Power Management Control Register (mpmc)                                        | 40 |

|------|--------|---------------------------------------------------------------------------------|----|

| 5.5  | 5.2    | Core Pause Control Register (mcpc)                                              | 40 |

| 6 Ex | ternal | Interrupts                                                                      | 42 |

| 6.1  | Fea    | tures                                                                           | 42 |

| 6.2  | Nar    | ning Convention                                                                 | 42 |

| 6.2  | 2.1    | Unit, Signal, and Register Naming                                               | 42 |

| 6.2  | 2.2    | Address Map Naming                                                              | 42 |

| 6.3  | Ove    | rview of Major Functional Units                                                 | 42 |

| 6.3  | 3.1    | External Interrupt Source                                                       | 42 |

| 6.3  | 3.2    | Gateway                                                                         | 42 |

| 6.3  | 3.3    | PIC Core                                                                        | 43 |

| 6.3  | 3.4    | Interrupt Target                                                                | 43 |

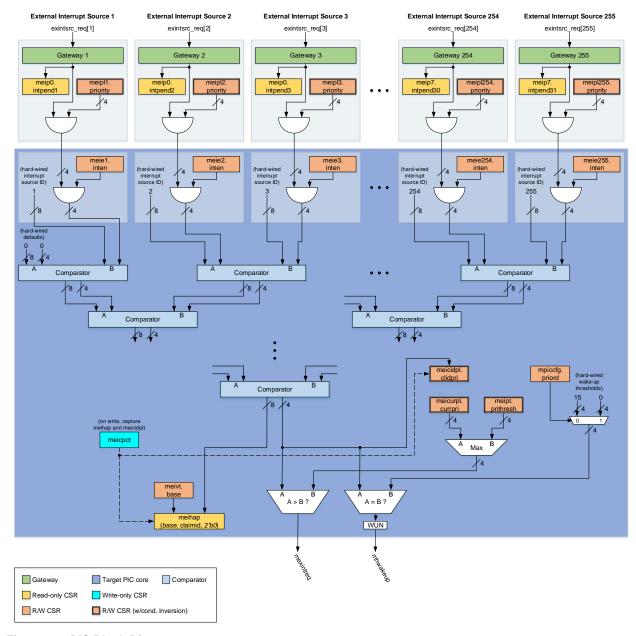

| 6.4  | PIC    | Block Diagram                                                                   | 43 |

| 6.5  | The    | ory of Operation                                                                | 46 |

| 6.5  | 5.1    | Initialization                                                                  | 46 |

| 6.5  | 5.2    | Regular Operation                                                               | 46 |

| 6.6  | Sup    | port for Vectored External Interrupts                                           | 47 |

| 6.6  | 6.1    | Full Hardware Implementation of Vectored External Interrupts                    | 48 |

| 6.7  | Inte   | rrupt Chaining                                                                  | 49 |

| 6.8  | Inte   | rrupt Nesting                                                                   | 49 |

| 6.9  | Per    | formance Targets                                                                | 50 |

| 6.10 | С      | onfigurability                                                                  | 50 |

| 6.1  | 0.1    | Rules                                                                           | 50 |

| 6.1  | 0.2    | Build Arguments                                                                 | 50 |

| 6.1  | 0.3    | Impact on Generated Code                                                        | 50 |

| 6.11 | Р      | IC Control/Status Registers                                                     | 51 |

| 6.1  | 1.1    | PIC Configuration Register (mpiccfg)                                            | 51 |

| 6.1  | 1.2    | External Interrupt Priority Level Registers (meiplS)                            | 51 |

| 6.1  | 1.3    | External Interrupt Pending Registers (meip X)                                   | 52 |

| 6.1  | 1.4    | External Interrupt Enable Registers (meie S)                                    | 52 |

| 6.1  | 1.5    | External Interrupt Priority Threshold Register (meipt)                          | 53 |

| 6.1  | 1.6    | External Interrupt Vector Table Register (meivt)                                | 53 |

| 6.1  | 1.7    | External Interrupt Handler Address Pointer Register (meihap)                    | 53 |

| 6.1  | 1.8    | External Interrupt Claim ID / Priority Level Capture Trigger Register (meicpct) | 54 |

| 6.1  | 1.9    | External Interrupt Claim ID's Priority Level Register (meicidpl)                | 54 |

| 6.1  | 1.10   | External Interrupt Current Priority Level Register (meicurpl)                   | 55 |

| 6.1  | 1.11   | External Interrupt Gateway Configuration Registers (meigwctrl S)                | 55 |

| 6.1  | 1.12   | External Interrupt Gateway Clear Registers (meigwclrS)                          | 56 |

| 6.12 | Р      | IC CSR Address Map                                                              | 56 |

| 6.13 | Р      | IC Memory-mapped Register Address Map                                           | 56 |

|    | 6.14 I  | nterrupt Enable/Disable Code Samples                                         | 57 |

|----|---------|------------------------------------------------------------------------------|----|

|    | 6.14.1  | Example Interrupt Flows                                                      | 57 |

|    | 6.14.2  | Example Interrupt Macros                                                     | 58 |

| 7  | Perforn | nance Monitoring                                                             | 60 |

|    | 7.1 Fe  | atures                                                                       | 60 |

|    | 7.2 Co  | ntrol/Status Registers                                                       | 60 |

|    | 7.2.1   | Standard RISC-V Registers                                                    | 60 |

|    | 7.2.2   | Platform-specific Control/Status Registers                                   | 60 |

|    | 7.3 Co  | unters                                                                       | 60 |

|    | 7.4 Co  | unt-Impacting Conditions                                                     | 61 |

|    | 7.5 Ev  | ents                                                                         | 61 |

| 8  | Cache   | Control                                                                      | 64 |

|    | 8.1 Fe  | atures                                                                       | 64 |

|    | 8.2 Fe  | ature Descriptions                                                           | 64 |

|    | 8.2.1   | Cache Flushing                                                               | 64 |

|    | 8.2.2   | Enabling/Disabling I-Cache                                                   | 64 |

|    | 8.2.3   | Diagnostic Access                                                            | 64 |

|    | 8.3 Us  | e Cases                                                                      | 64 |

|    | 8.4 Th  | eory of Operation                                                            | 65 |

|    | 8.4.1   | Read a Chunk of an I-cache Cache Line                                        | 65 |

|    | 8.4.2   | Write a Chunk of an I-cache Cache Line                                       | 65 |

|    | 8.4.3   | Read or Write a Full I-cache Cache Line                                      | 65 |

|    | 8.4.4   | Read a Tag and Status Information of an I-cache Cache Line                   | 65 |

|    | 8.4.5   | Write a Tag and Status Information of an I-cache Cache Line                  |    |

|    | 8.5 I-C | ache Control/Status Registers                                                | 66 |

|    | 8.5.1   | I-Cache Array/Way/Index Selection Register (dicawics)                        | 66 |

|    | 8.5.2   | I-Cache Array Data 0 Register (dicad0)                                       | 67 |

|    | 8.5.3   | I-Cache Array Data 1 Register (dicad1)                                       | 68 |

|    | 8.5.4   | I-Cache Array Go Register (dicago)                                           | 69 |

| 9  | SweRV   | EH1 Debug Support                                                            | 70 |

| !  | 9.1 Co  | ntrol/Status Registers                                                       | 70 |

|    | 9.1.1   | Control/Status Registers in JTAG Address Space                               | 70 |

|    | 9.1.2   | Control/Status Registers in Debug Module Interface Address Space             | 72 |

|    | 9.1.3   | Control/Status Registers in RISC-V CSR Address Space                         | 81 |

| 10 | Low-    | Level Core Control                                                           | 86 |

|    | 10.1    | Control/Status Registers                                                     | 86 |

|    | 10.1.1  | Feature Disable Control Register (mfdc)                                      | 86 |

|    | 10.1.2  | Clock Gating Control Register (mcgc)                                         | 87 |

| 11 | Stand   | dard RISC-V CSRs with Core-Specific Adaptations                              | 89 |

|    | 11.1.1  | Machine Interrupt Enable (mie) and Machine Interrupt Pending (mip) Registers | 89 |

| 11.1.2 Machine Cause Register (mcause)                                 | 90  |

|------------------------------------------------------------------------|-----|

| 12 CSR Address Map                                                     | 91  |

| 12.1 Standard RISC-V CSRs                                              | 91  |

| 12.2 Non-Standard RISC-V CSRs                                          | 92  |

| 13 Interrupt Priorities                                                | 94  |

| 14 Clock and Reset                                                     | 95  |

| 14.1 Features                                                          | 95  |

| 14.2 Clocking                                                          | 95  |

| 14.2.1 Regular Operation                                               | 95  |

| 14.2.2 System Bus-to-Core Clock Ratios                                 | 95  |

| 14.2.3 Asynchronous Signals                                            | 97  |

| 14.3 Reset                                                             | 98  |

| 14.3.1 Core Complex Reset (rst_l)                                      | 98  |

| 14.3.2 Debug Module Reset (dbg_rst_l)                                  | 99  |

| 14.3.3 Debugger Initiating Reset via JTAG Interface                    | 99  |

| 14.3.4 Core Complex Reset to Debug Mode                                | 99  |

| 15 SweRV EH1 Core Complex Port List                                    | 100 |

| 16 SweRV EH1 Core Build Arguments                                      | 109 |

| 16.1 Memory Protection Build Arguments                                 | 109 |

| 16.1.1 Memory Protection Build Argument Rules                          | 109 |

| 16.1.2 Memory Protection Build Arguments                               | 109 |

| 16.2 Core Memory-Related Build Arguments                               | 109 |

| 16.2.1 Core Memories and Memory-Mapped Register Blocks Alignment Rules | 109 |

| 16.2.2 Memory-Related Build Arguments                                  | 109 |

| 17 SweRV EH1 Compliance Test Suite Failures                            | 111 |

| 17.1 I-MISALIGN_LDST-01                                                | 111 |

| 17.2 I-MISALIGN_JMP-01                                                 | 111 |

| 17.3 I-FENCE.I-01 and fence_i                                          | 111 |

| 17.4 breakpoint                                                        | 112 |

| 18 SweRV EH1 Errata                                                    | 113 |

| 18.1 Back-to-back Write Transactions Not Supported on AHB-Lite Bus     | 113 |

| 18.2 Debug Write to minstret Register Stores Incremented Value         | 113 |

| 18.3 Debug Abstract Command Register May Return Non-Zero Value on Read | 113 |

## **List of Figures**

| Figure 1-1 SweRV EH1 Core Complex                                                  | 1  |

|------------------------------------------------------------------------------------|----|

| Figure 1-2 SweRV EH1 Core Pipeline                                                 | 2  |

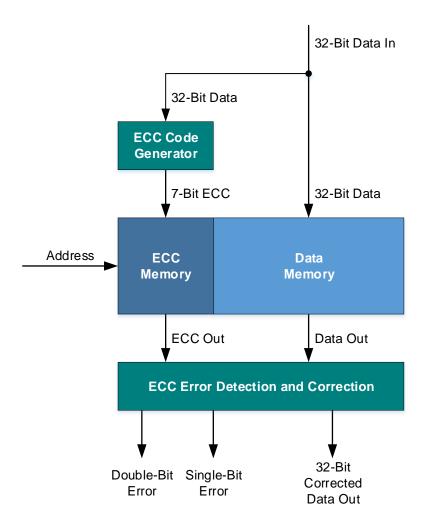

| Figure 3-1 Conceptual Block Diagram – ECC in a Memory System                       | 19 |

| Figure 5-1 SweRV EH1 Core Activity States                                          | 29 |

| Figure 5-2 SweRV EH1 Power and Multi-Core Debug Control and Status Signals         | 33 |

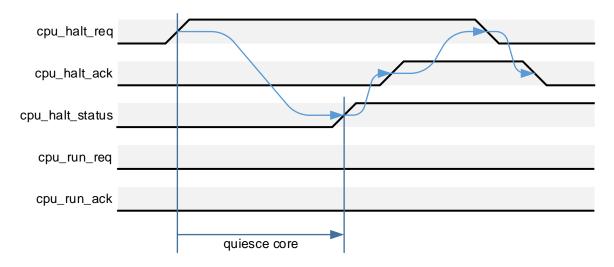

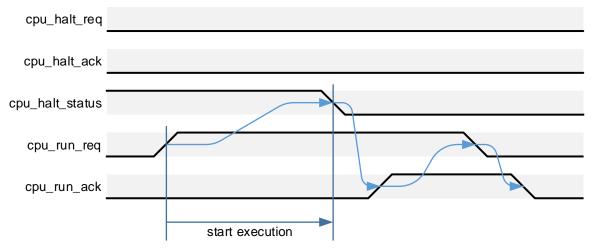

| Figure 5-3 SweRV EH1 Power Control and Status Interface Timing Diagrams            | 34 |

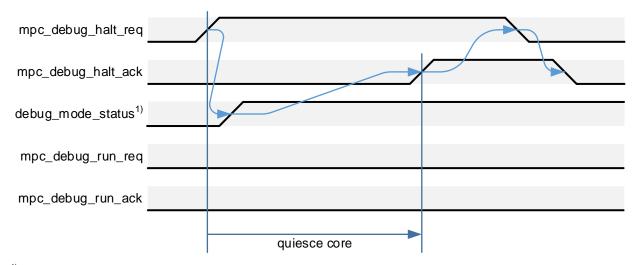

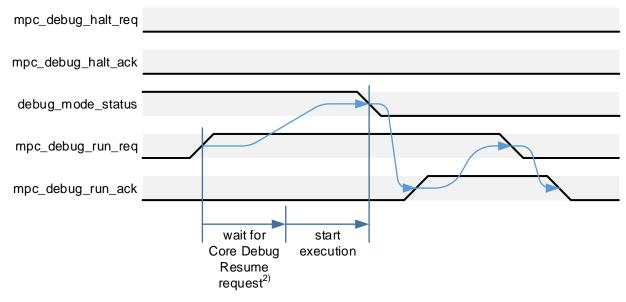

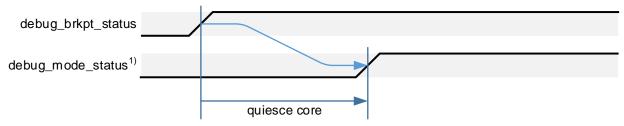

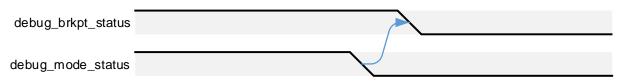

| Figure 5-4 SweRV EH1 Multi-Core Debug Control and Status Interface Timing Diagrams | 37 |

| Figure 5-5 SweRV EH1 Breakpoint Indication Timing Diagrams                         | 38 |

| Figure 6-1 PIC Block Diagram                                                       | 44 |

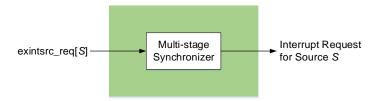

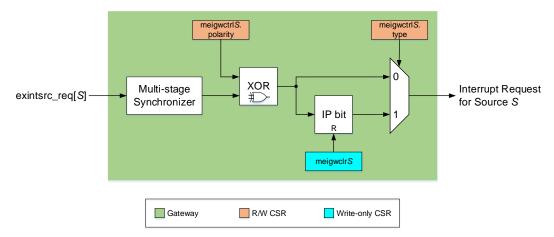

| Figure 6-2 Gateway for Asynchronous, Level-triggered Interrupt Sources             | 45 |

| Figure 6-3 Conceptual Block Diagram of a Configurable Gateway                      | 45 |

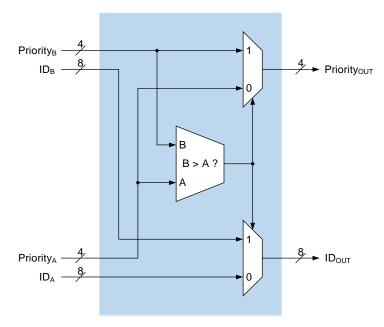

| Figure 6-4 Comparator                                                              | 45 |

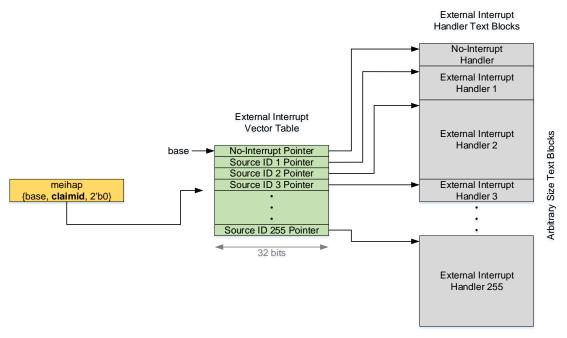

| Figure 6-5 Vectored External Interrupts                                            | 48 |

| Figure 6-6 Concept of Interrupt Chaining                                           | 49 |

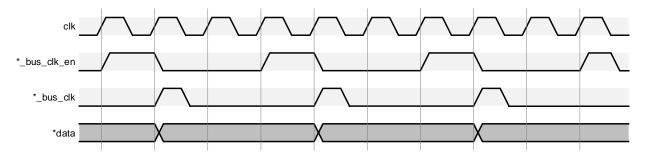

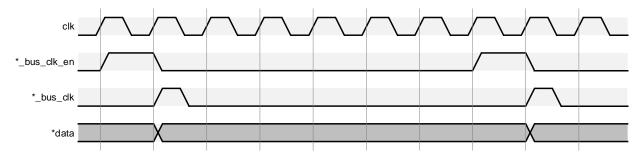

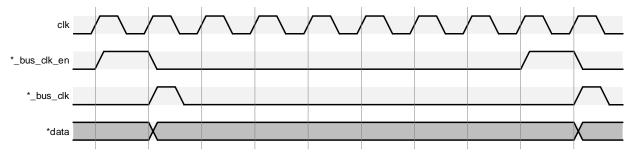

| Figure 14-1 Conceptual Clock, Clock-Enable, and Data Timing Relationship           | 95 |

| Figure 14-2 1:1 System Bus-to-Core Clock Ratio                                     | 96 |

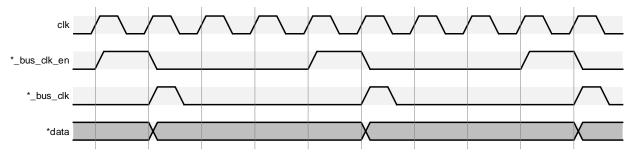

| Figure 14-3 1:2 System Bus-to-Core Clock Ratio                                     | 96 |

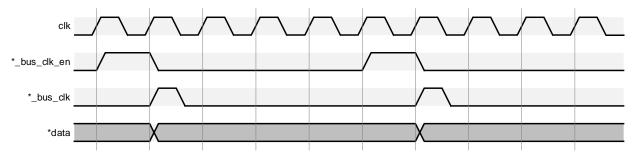

| Figure 14-4 1:3 System Bus-to-Core Clock Ratio                                     | 96 |

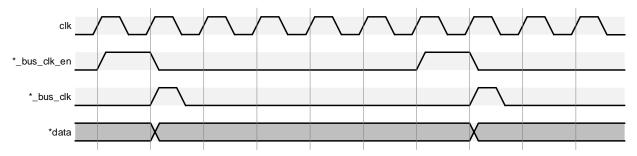

| Figure 14-5 1:4 System Bus-to-Core Clock Ratio                                     | 96 |

| Figure 14-6 1:5 System Bus-to-Core Clock Ratio                                     | 97 |

| Figure 14-7 1:6 System Bus-to-Core Clock Ratio                                     | 97 |

| Figure 14-8 1:7 System Bus-to-Core Clock Ratio                                     | 97 |

| Figure 14-9 1:8 System Bus-to-Core Clock Ratio                                     | 97 |

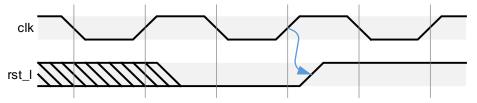

| Figure 14-10 Conceptual Clock and Reset Timing Relationship                        | 98 |

## **List of Tables**

| Table 2-1             | Access Properties for each Memory Type                                                        | 4  |

|-----------------------|-----------------------------------------------------------------------------------------------|----|

| Table 2-2             | Handling of Unmapped Addresses                                                                | 8  |

| Table 2-3             | Handling of Misaligned Accesses                                                               | 9  |

| Table 2-4             | Handling of Uncorrectable ECC Errors                                                          | 10 |

| Table 2-5             | Handling of Correctable ECC/Parity Errors                                                     | 11 |

| Table 2-6             | Region Access Control Register (mrac, at CSR 0x7C0)                                           | 13 |

| Table 2-7             | Memory Synchronization Trigger Register (dmst, at CSR 0x7C4)                                  | 13 |

| Table 2-8             | D-Bus First Error Address Capture Register (mdseac, at CSR 0xFC0)                             | 14 |

| Table 2-9             | D-Bus Error Address Unlock Register (mdeau, at CSR 0xBC0)                                     | 14 |

| Table 2-10            | SweRV EH1 Memory Address Map (Example)                                                        | 14 |

| Table 2-1             | 1 Summary of NMI mcause Values                                                                | 17 |

| Table 3-1             | Memory Hierarchy Components and Protection                                                    | 20 |

| Table 3-2             | Error Detection, Recovery, and Logging                                                        | 21 |

| Table 3-3             | I-Cache Error Counter/Threshold Register (micect, at CSR 0x7F0)                               | 23 |

| Table 3-4             | ICCM Correctable Error Counter/Threshold Register (miccmect, at CSR 0x7F1)                    | 23 |

| Table 3-5             | DCCM Correctable Error Counter/Threshold Register (mdccmect, at CSR 0x7F2)                    | 24 |

| Table 4-1             | Internal Timer Counter 0 / 1 Register (mitcnt0/1, at CSR 0x7D2 / 0x7D5)                       | 26 |

| Table 4-2             | Internal Timer Bound 0 / 1 Register (mitb0/1, at CSR 0x7D3 / 0x7D6)                           | 26 |

| Table 4-3             | Internal Timer Control 0 / 1 Register (mitctl0/1, at CSR 0x7D4 / 0x7D7)                       | 26 |

| Table 5-1             | Debug Resume Requests                                                                         | 30 |

| Table 5-2             | Core Activity States                                                                          | 31 |

| Table 5-3             | SweRV EH1 Power Control and Status Signals                                                    | 33 |

| Table 5-4             | SweRV EH1 Multi-Core Debug Control and Status Signals                                         | 35 |

| Table 5-5             | Power Management Control Register (mpmc, at CSR 0x7C6)                                        | 40 |

| Table 5-6             | Core Pause Control Register (mcpc, at CSR 0x7C2)                                              | 41 |

| Table 6-1             | PIC Configuration Register (mpiccfg, at PIC_base_addr+0x3000)                                 | 51 |

| Table 6-2             | External Interrupt Priority Level Register S=1255 (meiplS, at PIC_base_addr+S*4)              | 52 |

| Table 6-3             | External Interrupt Pending Register X=07 (meipX, at PIC_base_addr+0x1000+X*4)                 | 52 |

| Table 6-4             | External Interrupt Enable Register S=1255 (meieS, at PIC_base_addr+0x2000+S*4)                | 52 |

| Table 6-5             | External Interrupt Priority Threshold Register (meipt, at CSR 0xBC9)                          | 53 |

| Table 6-6             | External Interrupt Vector Table Register (meivt, at CSR 0xBC8)                                | 53 |

| Table 6-7             | External Interrupt Handler Address Pointer Register (meihap, at CSR 0xFC8)                    | 54 |

| Table 6-8             | External Interrupt Claim ID / Priority Level Capture Trigger Register (meicpct, at CSR 0xBCA) | 54 |

| Table 6-9             | External Interrupt Claim ID's Priority Level Register (meicidpl, at CSR 0xBCB)                | 55 |

| Table 6-10            | External Interrupt Current Priority Level Register (meicurpl, at CSR 0xBCC)                   | 55 |

| Table 6-1<br>PIC_base | 1 External Interrupt Gateway Configuration Register S=1255 (meigwctrlS, ataddr+0x4000+S*4)    | 55 |

|                       | 2 External Interrupt Gateway Clear Register S=1255 (meigwclrS, at PIC_base_addr+0x5000+S*4)   |    |

| Table 6-13 PIC Non-standard RISC-V CSR Address Map                                           | 56 |

|----------------------------------------------------------------------------------------------|----|

| Table 6-14 PIC Memory-mapped Register Address Map                                            | 56 |

| Table 7-1 Group Performance Monitor Control Register (mgpmc, at CSR 0x7D0)                   | 60 |

| Table 7-2 List of Countable Events                                                           | 61 |

| Table 8-1 I-Cache Array/Way/Index Selection Register (dicawics, at CSR 0x7C8)                | 66 |

| Table 8-2 I-Cache Array Data 0 Register (dicad0, at CSR 0x7C9)                               | 67 |

| Table 8-3 I-Cache Array Data 1 Register (dicad1, at CSR 0x7CA)                               | 68 |

| Table 8-4 I-Cache Array Go Register (dicago, at CSR 0x7CB)                                   | 69 |

| Table 9-1 Registers in JTAG Debug Transport Module Address Space                             | 70 |

| Table 9-2 IDCODE Register (IDCODE, at JTAG 0x01)                                             | 71 |

| Table 9-3 DTM Control and Status Register (dtmcs, at JTAG 0x10)                              | 71 |

| Table 9-4 Debug Module Interface Access Register (dmi, at JTAG 0x11)                         | 72 |

| Table 9-5 BYPASS Register (BYPASS, at JTAG 0x1F)                                             | 72 |

| Table 9-6 Registers in Debug Module Interface Address Space                                  | 73 |

| Table 9-7 Debug Module Control Register (dmcontrol, at Debug Module Offset 0x10)             | 73 |

| Table 9-8 Debug Module Status Register (dmstatus, at Debug Module Offset 0x11)               | 74 |

| Table 9-9 Halt Summary 0 Register (haltsum0, at Debug Module Offset 0x40)                    | 75 |

| Table 9-10 Abstract Control and Status Register (abstractcs, at Debug Module Offset 0x16)    | 76 |

| Table 9-11 Abstract Command Register (command, at Debug Module Offset 0x17)                  | 77 |

| Table 9-12 Abstract Data 0 / 1 Register (data0/1, at Debug Module Offset 0x04 / 0x05)        | 78 |

| Table 9-13 System Bus Access Control and Status Register (sbcs, at Debug Module Offset 0x38) | 78 |

| Table 9-14 System Bus Address 31:0 Register (sbaddress0, at Debug Module Offset 0x39)        | 80 |

| Table 9-15 System Bus Data 31:0 Register (sbdata0, at Debug Module Offset 0x3C)              | 80 |

| Table 9-16 System Bus Data 63:32 Register (sbdata1, at Debug Module Offset 0x3D)             | 81 |

| Table 9-17 Trigger Select Register (tselect, at CSR 0x7A0)                                   | 81 |

| Table 9-18 Trigger Data 1 Register (tdata1, at CSR 0x7A1)                                    | 81 |

| Table 9-19 Match Control Register (mcontrol, at CSR 0x7A1)                                   | 82 |

| Table 9-20 Trigger Data 2 Register (tdata2, at CSR 0x7A2)                                    | 83 |

| Table 9-21 Debug Control and Status Register (dcsr, at CSR 0x7B0)                            | 83 |

| Table 9-22 Debug PC Register (dpc, at CSR 0x7B1)                                             | 85 |

| Table 10-1 Feature Disable Control Register (mfdc, at CSR 0x7F9)                             | 86 |

| Table 10-2 Clock Gating Control Register (mcgc, at CSR 0x7F8)                                | 87 |

| Table 11-1 Machine Interrupt Enable Register (mie, at CSR 0x304)                             | 89 |

| Table 11-2 Machine Interrupt Pending Register (mip, at CSR 0x344)                            | 89 |

| Table 11-3 Machine Cause Register (mcause, at CSR 0x342)                                     | 90 |

| Table 12-1 SweRV EH1 Core-Specific Standard RISC-V Machine Information CSRs                  | 91 |

| Table 12-2 SweRV EH1 Standard RISC-V CSR Address Map                                         | 91 |

| Table 12-3 SweRV EH1 Non-Standard RISC-V CSR Address Map                                     | 92 |

| Table 13-1 SweRV EH1 Platform-specific and Standard RISC-V Interrupt Priorities              | 94 |

| Table 14-1 Core Complex Asynchronous Signals                                                 | 98 |

| RISC-V SweRV™ EH1 Programmer's Reference Manual -Rev. 1.6- | 5/15/2020 |

|------------------------------------------------------------|-----------|

|                                                            |           |

| Table 15-1 Core Complex Signals                            | 100       |

## **Reference Documents**

| Item #      | Document                                                             | Revision Used                      | Comment                             |

|-------------|----------------------------------------------------------------------|------------------------------------|-------------------------------------|

| 1           | The RISC-V Instruction Set Manual Volume I: User-Level ISA           | 20190305-Base-Ratification         |                                     |

| 2           | The RISC-V Instruction Set Manual Volume II: Privileged Architecture | 20190405-Priv-MSU-<br>Ratification |                                     |

| 2<br>(PLIC) | The RISC-V Instruction Set Manual Volume II: Privileged Architecture | 1.11-draft<br>December 1, 2018     | Last spec version with PLIC chapter |

| 3           | RISC-V External Debug Support                                        | 0.13.2                             | Spec ratified                       |

## **Abbreviations**

| Abbreviation | Description                                            |

|--------------|--------------------------------------------------------|

| AHB          | Advanced High-performance Bus (by ARM®)                |

| AMBA         | Advanced Microcontroller Bus Architecture (by ARM)     |

| ASIC         | Application Specific Integrated Circuit                |

| AXI          | Advanced eXtensible Interface (by ARM)                 |

| ССМ          | Closely Coupled Memory (= TCM)                         |

| CPU          | Central Processing Unit                                |

| CSR          | Control and Status Register                            |

| DCCM         | Data Closely Coupled Memory (= DTCM)                   |

| DEC          | DECoder unit (part of core)                            |

| DMA          | Direct Memory Access                                   |

| DTCM         | Data Tightly Coupled Memory (= DCCM)                   |

| ECC          | Error Correcting Code                                  |

| EXU          | EXecution Unit (part of core)                          |

| ICCM         | Instruction Closely Coupled Memory (= ITCM)            |

| IFU          | Instruction Fetch Unit                                 |

| ITCM         | Instruction Tightly Coupled Memory (= ICCM)            |

| JTAG         | Joint Test Action Group                                |

| LSU          | Load/Store Unit (part of core)                         |

| NMI          | Non-Maskable Interrupt                                 |

| PIC          | Programmable Interrupt Controller                      |

| PLIC         | Platform-Level Interrupt Controller                    |

| POR          | Power-On Reset                                         |

| RAM          | Random Access Memory                                   |

| RAS          | Return Address Stack                                   |

| ROM          | Read-Only Memory                                       |

| SECDED       | Single-bit Error Correction/Double-bit Error Detection |

| SEDDED       | Single-bit Error Detection/Double-bit Error Detection  |

| SoC          | System on Chip                                         |

| TBD          | To Be Determined                                       |

| TCM          | Tightly Coupled Memory (= CCM)                         |

#### 1 SweRV EH1 Core Overview

This chapter provides a high-level overview of the SweRV EH1 core and core complex. SweRV EH1 is a machine-mode (M-mode) only, 32-bit CPU core which supports RISC-V's integer (I), compressed instruction (C), multiplication and division (M), and instruction-fetch fence and CSR instructions (Z) extensions, (i.e., RV32IMCZicsr\_Zifencei). The core is a 9-stage, dual-issue, superscalar, mostly in-order pipeline with some out-of-order execution capability.

#### 1.1 Features

The SweRV EH1 core complex's feature set includes:

- RV32IMCZicsr\_Zifencei-compliant RISC-V core with branch predictor

- Optional instruction and data closely-coupled memories with ECC protection

- Optional 4-way set-associative instruction cache with parity or ECC protection

- Optional programmable interrupt controller supporting up to 255 external interrupts

- Four system bus interfaces for instruction fetch, data accesses, debug accesses, and external DMA accesses to closely-coupled memories (configurable as 64-bit AXI4 or AHB-Lite)

- Core debug unit compliant with the RISC-V Debug specification [3]

- 1GHz target frequency (for 28nm technology node)

#### 1.2 Core Complex

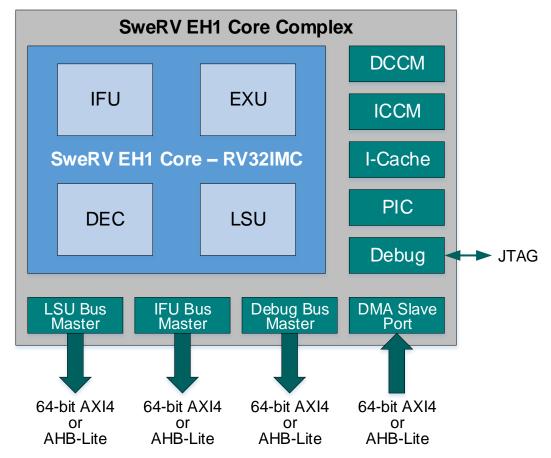

Figure 1-1 depicts the core complex and its functional blocks which are described further in Section 1.3.

Figure 1-1 SweRV EH1 Core Complex

#### 1.3 Functional Blocks

The SweRV EH1 core complex's functional blocks are described in the following sections in more detail.

#### 1.3.1 Core

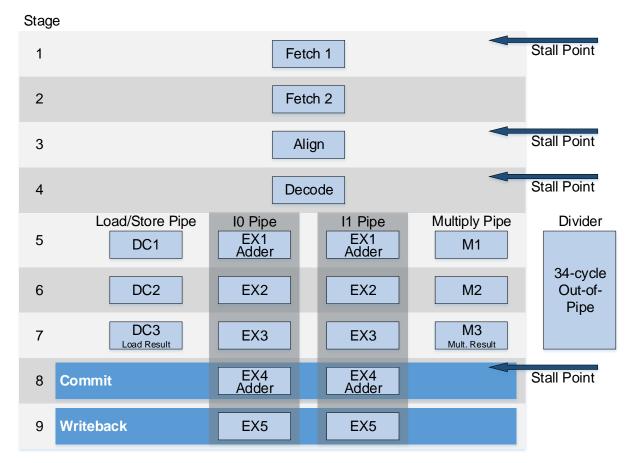

Figure 1-2 depicts the superscalar, dual-issue 9-stage core pipeline supporting four arithmetic logic units (ALUs) labeled EX1 and EX4 in two pipelines I0 and I1, one load/store pipeline, one 3-cycle latency multiplier pipeline, and one out-of-pipeline 34-cycle latency divider. There are four stall points in the pipeline: 'Fetch1', 'Align', 'Decode', and 'Commit'. In the 'Align' stage, instructions are formed from 3 fetch buffers. In the 'Decode' stage, up to 2 instructions from 4 instruction buffers are decoded. In the 'Commit' stage, up to 2 instructions per cycle are committed. Finally, in the 'Writeback' stage, the architectural registers are updated.

Figure 1-2 SweRV EH1 Core Pipeline

#### 2 Memory Map

This chapter describes the memory map as well as the various memories and their properties of the SweRV EH1 core.

#### 2.1 Address Regions

The 32-bit address space is subdivided into sixteen fixed-sized, contiguous 256MB regions. Each region has a set of access control bits associated with it (see Section 2.8.1).

#### 2.2 Access Properties

Each region has two access properties which can be independently controlled. They are:

- Cacheable: Indicates if this region is allowed to be cached or not.

- Side effect: Indicates if read/write accesses to this region may have side effects (i.e., non-idempotent

accesses which may potentially have side effects on any read/write access; typical for I/O, speculative or

redundant accesses must be avoided) or have no side effects (i.e., idempotent accesses which have no side

effects even if the same access is performed multiple times; typical for memory). Note that stores with

potential side effects (i.e., to non-idempotent addresses) cannot be combined with other stores in the core's

write buffer.

#### 2.3 Memory Types

There are two different classes of memory types mapped into the core's 32-bit address range, core local and system bus attached.

#### 2.3.1 Core Local

#### 2.3.1.1 ICCM and DCCM

Two dedicated memories, one for instruction and the other for data, are tightly coupled to the core. These memories provide low-latency access and SECDED ECC protection. Their respective sizes (4, 8, 16, 32, 48<sup>1</sup>, 64, 128, 256, or 512KB) are set as arguments at build time of the core.

#### 2.3.1.2 Local Memory-mapped Control/Status Registers

To provide control for regular operation, the core requires a number of memory-mapped control/status registers. For example, some external interrupt functions are controlled and serviced with accesses to various registers while the system is running.

#### 2.3.2 Accessed via System Bus

#### 2.3.2.1 System ROMs

The SoC may host ROMs which are mapped to the core's memory address range and accessed via the system bus. Both instruction and data accesses are supported to system ROMs.

#### 2.3.2.2 System SRAMs

The SoC hosts a variety of SRAMs which are mapped to the core's memory address range and accessed via the system bus.

#### 2.3.2.3 System Memory-mapped I/O

The SoC hosts a variety of I/O device interfaces which are mapped to the core's memory address range and accessed via the system bus.

-

<sup>&</sup>lt;sup>1</sup> DCCM only

#### 2.3.3 Mapping Restrictions

Core-local memories and system bus-attached memories must be mapped to different regions. Mapping both classes of memory types to the same region is not allowed.

Furthermore, it is recommended that all core-local memories are mapped to the same region.

#### 2.4 Memory Type Access Properties

Table 2-1 specifies the access properties of each memory type. During system boot, firmware must initialize the properties of each region based on the memory type present in that region.

Note that some memory-mapped I/O and control/status registers may have no side effects (i.e., are idempotent), but characterizing all these registers as having potentially side effects (i.e., are non-idempotent) is safe.

Table 2-1 Access Properties for each Memory Type

| Memory Type                            | Cacheable | Side Effect |

|----------------------------------------|-----------|-------------|

| Core Local                             |           |             |

| ICCM                                   | No        | No          |

| DCCM                                   | No        | No          |

| Memory-mapped control/status registers | No        | Yes         |

| Accessed via System Bus                |           |             |

| ROMs                                   | Yes       | No          |

| SRAMs                                  | Yes       | No          |

| I/Os                                   | No        | Yes         |

| Memory-mapped control/status registers | No        | Yes         |

**Note:** 'Cacheable = Yes' and 'Side Effect = Yes' is an illegal combination.

#### 2.5 Memory Access Ordering

Loads and stores to system bus-attached memory (i.e., accesses with no side effects, idempotent) and devices (i.e., accesses with potential side effects, non-idempotent) go through a read buffer and a write buffer, respectively. The buffers are implemented as FIFOs.

#### 2.5.1 Load-to-Load and Store-to-Store Ordering

All loads are sent to the system bus interface in program order. Also, all stores are sent to the system bus interface in program order.

#### 2.5.2 Load/Store Ordering

#### 2.5.2.1 Accesses with Potential Side Effects (i.e., Non-Idempotent)

When a load with potential side effects (i.e., non-idempotent) enters the read buffer, the entire write buffer is emptied, i.e., both stores with no side effects (i.e., idempotent) and with potential side effects (i.e., non-idempotent) are drained out. Loads with potential side effects (i.e., non-idempotent) are sent out to the system bus with their exact size.

Stores with potential side effects (i.e., non-idempotent) are neither coalesced nor forwarded to a load.

#### 2.5.2.2 Accesses with No Side Effects (i.e., Idempotent)

Loads with no side effects (i.e., idempotent) are always issued as double-words and check the contents of the write buffer:

- 1. **Full address match** (all load bytes present in the write buffer): Data is forwarded from the write buffer. The load does not freeze the pipe and won't go out to the system bus.

- 2. **Partial address match** (some of the load bytes are in the write buffer): The entire write buffer is emptied, then the load request goes to the system bus.

- 3. **No match** (none of the bytes are in the write buffer): The load is presented to the system bus interface without waiting for the stores to drain.

#### 2.5.2.3 Ordering of Store - Load with No Side Effects (i.e., Idempotent)

A fence instruction is required to order an older store before a younger load with no side effects (i.e., idempotent).

**Note:** All memory-mapped register writes must be followed by a fence instruction to enforce ordering and synchronization.

#### 2.5.3 Fencing

#### 2.5.3.1 Instructions

The fence.i instruction operates on the instruction memory and/or I-cache. This instruction causes a flush, a flash invalidation of the I-cache, and a refetch of the next program counter (RFNPC). The refetch is guaranteed to miss the I-cache. Note that since the fence.i instruction is used to synchronize the instruction and data streams, it also includes the functionality of the fence instruction (see Sections 2.5.3.2 and 2.5.3.3).

#### 2.5.3.2 Data

The fence instruction is implemented conservatively in SweRV EH1 to keep the implementation simple. It always performs the most conservative fencing, independent of the instruction's arguments. The fence instruction is presynced to make sure that there are no instructions in the LSU pipe. It stalls until the LSU indicates that the read buffer has been cleared, the store and write buffers have been fully drained (i.e., are empty), and the bus barrier (see Section 2.5.3.3) is finished. The fence instruction is only committed after all LSU buffers are idle and all outstanding bus transactions are completed.

#### 2.5.3.3 Bus Barrier

SweRV EH1 provides a bus barrier mechanism. Executing a fence instruction forces a bus synchronization action which requires all outstanding bus transactions (reads and writes) for the LSU bus master to complete.

Hardware uses an 8-bit counter with which it continuously keeps track of the number of outstanding bus transactions. For every request sent, this counter is incremented; for every response received, this counter is decremented. The maximum number of outstanding bus transactions is 255. If this limit is reached, no further transactions are sent to the bus until the number of outstanding bus transactions is smaller than 255. A bus barrier requires the count to reach 0 before the barrier is finished.

Loads are not allowed to be forwarded across an older bus barrier. The LSU enforces this within the core pipeline. Also, the LSU does not forward from the write buffer if the buffer itself contains a bus barrier.

The fence instruction leverages the semantics of the bus barrier. A fence instruction waits for all prior bus transactions to finish in addition to the write buffer being fully drained before proceeding. Instructions after a fence.i are guaranteed to see previous writes in the case of self-modifying code.

#### 2.5.4 Imprecise Data Bus Errors

All store errors as well as non-blocking load errors on the system bus are imprecise. The address of the first occurring imprecise data system bus error is logged and a non-maskable interrupt (NMI) is flagged for the first reported error only. For stores, if there are other stores in the write buffer behind the store which had the error, these stores are sent out on the system bus and any error responses are ignored. Similarly, for non-blocking loads, any error responses on subsequent loads sent out on the system bus are ignored. NMIs are fatal, architectural state is lost, and the core needs to be reset. The reset also unlocks the first error address capture register again.

**Note:** It is possible to unlock the first error address capture register with a write to an unlock register as well (see Section 2.8.4 for more details), but this may result in unexpected behavior.

#### 2.6 Memory Protection

To eliminate issuing speculative accesses to the IFU and LSU bus interfaces, SweRV EH1 provides a rudimentary memory protection mechanism for instruction and data accesses outside of the ICCM and DCCM memory regions. Separate core build arguments for instructions and data are provided to enable and configure up to 8 address windows each.

An instruction fetch to a non-ICCM region must fall within the address range of at least one instruction access window for the access to be forwarded to the IFU bus interface. If at least one instruction access window is enabled, non-speculative fetch requests which are not within the address range of any enabled instruction access window cause a precise instruction access fault exception. If none of the 8 instruction access windows is enabled, the memory protection mechanism for instruction accesses is turned off. For the ICCM region, accesses within the ICCM's address range are allowed. However, any access not within the ICCM's address range results in a precise instruction access fault exception.

Similarly, a load/store access to a non-DCCM or non-PIC memory-mapped control register region must fall within the address range of at least one data access window for the access to be forwarded to the LSU bus interface. If at least one data access window is enabled, non-speculative load/store requests which are not within the address range of any enabled data access window cause a precise load/store address misaligned or access fault exception. If none of the 8 data access windows is enabled, the memory protection mechanism for data accesses is turned off. For the DCCM and PIC memory-mapped control register region(s), accesses within the DCCM's or the PIC memory-mapped control register's address range are allowed. However, any access not within the DCCM's or PIC memory-mapped control register's address range results in a precise load/store address misaligned or access fault exception.

The configuration parameters for each of the 8 instruction and 8 data access windows are:

- Enable/disable instruction/data access window 0..7,

- a base address of the window (which must be 64B-aligned), and

- a mask specifying the size of the window (which must be an integer-multiple of 64 bytes minus 1).

See Section 16.1 for more information.

#### 2.7 Exception Handling

Capturing the faulting effective address causing an exception helps assist firmware in handling the exception and/or provides additional information for firmware debugging. For precise exceptions, the faulting effective address is captured in the standard RISC-V mtval register (see Section 3.1.17 in [2]). For imprecise exceptions, the address of the first occurrence of the error is captured in a platform-specific error address capture register (see Section 2.8.3).

#### 2.7.1 Imprecise Bus Error Non-Maskable Interrupt

Store bus errors are fatal and cause a non-maskable interrupt (NMI). The store bus error NMI has an mcause value of 0xF000\_0000.

Likewise, non-blocking load bus errors are fatal and cause a non-maskable interrupt (NMI). The non-blocking load bus error NMI has an mcause value of 0xF000\_0001.

**Note:** The address of the first store or non-blocking load error on the D-bus is captured in the mdseac register (see Section 2.8.3). The register is unlocked either by resetting the core after the NMI has been handled or by a write to the mdeau register (see Section 2.8.4). While the mdseac register is locked, subsequent D-bus errors are gated (i.e., they do not cause another NMI), but NMI requests originating external to the core are still honored.

**Note:** If store and non-blocking load bus errors are reported in the same clock cycle (i.e., the LSU's write and read buffers simultaneous indicate a bus error), the non-blocking load bus error has higher priority.

#### 2.7.2 Correctable Error Local Interrupt

I-cache parity/ECC errors, ICCM correctable ECC errors, and DCCM correctable ECC errors are counted in separate correctable error counters (see Sections 3.5.1, 3.5.2, and 3.5.3, respectively). Each counter also has its separate programmable error threshold. If any of these counters has reached its threshold, a correctable error local interrupt is signaled. Firmware should determine which of the counters has reached the threshold and reset that counter.

A local-to-the-core interrupt for correctable errors has pending (*mceip*) and enable (*mceie*) bits in bit position 30 of the standard RISC-V mip (see Table 11-2) and mie (see Table 11-1) registers, respectively. The priority is lower than

RISC-V External interrupt, but higher than RISC-V Timer interrupt (see Table 13-1). The correctable error local interrupt has an mcause value of 0x8000\_001E (see Table 11-3).

#### 2.7.3 Rules for Core-Local Memory Accesses

The rules for instruction fetch and load/store accesses to core-local memories are:

- 1. An instruction fetch access to a region

- a. containing one or more ICCM sub-region(s) causes an exception if

- i. the access is not completely within the ICCM sub-region, or

- ii. the boundary of an ICCM to a non-ICCM sub-region and vice versa is crossed, even if the region contains a DCCM/PIC memory-mapped control register sub-region.

- b. not containing an ICCM sub-region goes out to the system bus, even if the region contains a DCCM/PIC memory-mapped control register sub-region.

- 2. A load/store access to a region

- a. containing one or more DCCM/PIC memory-mapped control register sub-region(s) causes an

exception if

- the access is not completely within the DCCM/PIC memory-mapped control register subregion, or

- ii. the boundary of

- 1. a DCCM to a non-DCCM sub-region and vice versa, or

- 2. a PIC memory-mapped control register sub-region

is crossed.

even if the region contains an ICCM sub-region.

**b.** not containing a DCCM/PIC memory-mapped control register sub-region goes out to the system bus, even if the region contains an ICCM sub-region.

## 2.7.4 Unmapped Addresses

Table 2-2 Handling of Unmapped Addresses

| Access       | Core/Bus | Side Effect | Action                                                       | Comments                                                                       |                                                |

|--------------|----------|-------------|--------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------|

| Fetch        | Core     | N/A         | Instruction access fault exception <sup>2,3</sup>            | Precise exception                                                              |                                                |

| reich        | Bus      | N/A         | Instruction access fault exception <sup>2</sup>              | (e.g., address out-of-range)                                                   |                                                |

|              | Core     | No          | Load access fault exception <sup>4,5</sup>                   | Precise exception (e.g., address out-of-range)                                 |                                                |

|              |          |             | Non-blocking load bus error NMI (see Section 2.7.1)          | Imprecise, fatal     Capture store address in core bus interface               |                                                |

| Load         | Bus      | b           | No<br>(for<br>blocking<br>load)                              | Load access fault exception                                                    | Precise exception (e.g., address out-of-range) |

|              |          | Yes         |                                                              | <ul><li> Precise exception</li><li> Hold off all external interrupts</li></ul> |                                                |

|              | Core     | No          | Store/AMO <sup>6</sup> access fault exception <sup>4,5</sup> | Precise exception                                                              |                                                |

| Store        |          | No          | Store bus error NMI                                          | Imprecise, fatal                                                               |                                                |

|              | Bus      | Yes         | (see Section 2.7.1)                                          | Capture store address in core bus interface                                    |                                                |

| DMA<br>Read  | Puo      | N/A         | DMA slave bus error                                          | Sand array response to meeter                                                  |                                                |

| DMA<br>Write | Bus      | IN/A        | DIVIA SIAVE DUS EFFOF                                        | Send error response to master                                                  |                                                |

**Note:** It is recommended to provide address gaps between different memories to ensure unmapped address exceptions are flagged if memory boundaries are inadvertently crossed.

Copyright © 2020 Western Digital Corporation or its affiliates; Licensed under Apache-2.0

<sup>&</sup>lt;sup>2</sup> If any byte of an instruction is from an unmapped address, an instruction access fault precise exception is flagged.

<sup>&</sup>lt;sup>3</sup> Exception also flagged for fetches to the DCCM address range if located in the same region, or if located in different regions and no SoC address is a match.

<sup>&</sup>lt;sup>4</sup> Exception also flagged for PIC load/store not word-sized or address not word-aligned.

<sup>&</sup>lt;sup>5</sup> Exception also flagged for loads/stores to the ICCM address range if located in the same region, or if located in different regions and no SoC address is a match.

<sup>&</sup>lt;sup>6</sup> AMO refers to the RISC-V "A" (atomics) extension, which is not implemented in SweRV EH1.

## 2.7.5 Misaligned Accesses

#### General notes:

- The core performs a misalignment check during the address calculation.

- Accesses across region boundaries always cause a misaligned exception.

- Splitting a load/store from/to an address with no side effects (i.e., idempotent) is not of concern for SweRV FH1.

Table 2-3 Handling of Misaligned Accesses

| Access                    | Core/Bus   | Side<br>Effect   | Region<br>Cross | Action                                        | Comments                      |  |

|---------------------------|------------|------------------|-----------------|-----------------------------------------------|-------------------------------|--|

| Fetch                     | Core       | N/A              |                 | N/A                                           | Not possible <sup>7</sup>     |  |

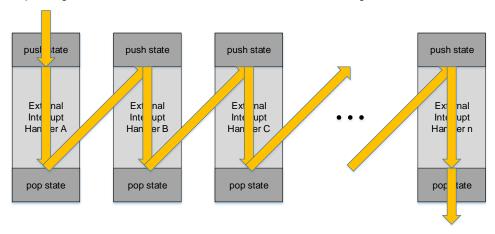

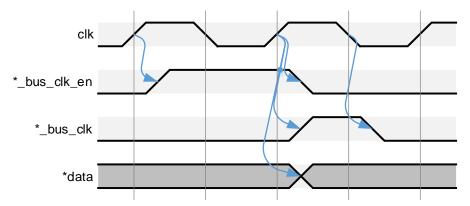

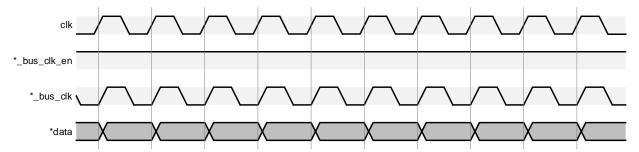

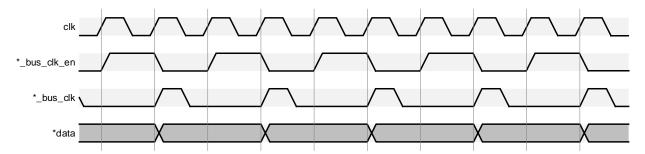

| reich                     | Bus        | N/A              |                 | IV/A                                          | Not possible                  |  |